# Clock OSC SG3225VAN

Product name SG3225VAN 125.003125MHz KJGA Product Number / Ordering code X1G0042410113xx

Please refer to the 9.Packing information about xx (last 2 digits)

Output waveform LVDS

Pb free / Complies with EU RoHS directive

Reference weight Typ. 25 mg

| 1.Absolute maximum ratings |         |      |      |         |      |                           |

|----------------------------|---------|------|------|---------|------|---------------------------|

| Parameter                  | Symbol  | Min. | Тур. | Max.    | Unit | Conditions / Remarks      |

| Maximum supply voltage     | Vcc-GND | -0.3 | -    | +4      | V    | -                         |

| Storage temperature        | T_stg   | -40  | -    | +125    | °C   | Storage as single product |

| Input voltage              | Vin     | -0.3 | -    | Vcc+0.3 | V    | OE Terminal               |

| Parameter                   | Symbol           | Min.     | Тур.     | Max.     | Unit                    | Conditions / Remarks                               |

|-----------------------------|------------------|----------|----------|----------|-------------------------|----------------------------------------------------|

| Output frequency            | f0               | -        | 125.0031 | -        | MHz                     |                                                    |

| Supply voltage              | Vcc              | 2.25     | -        | 3.63     | V                       | -                                                  |

| Operating temperature       | T_use            | -40      | -        | +85      | °C                      | -                                                  |

| Frequency tolerance         | f tol            | -50      | -        | 50       | x10 <sup>-6</sup>       | -                                                  |

| Current consumption         | Icc              | -        | -        | 30       | mA                      | OE = Vcc, L_LVDS = 100 Ω                           |

| Stand-by current            | I std            | -        | _        | _        | mA                      | -                                                  |

| Disable current             | I_dis            | -        | _        | 20.0     | mA                      | OE = GND                                           |

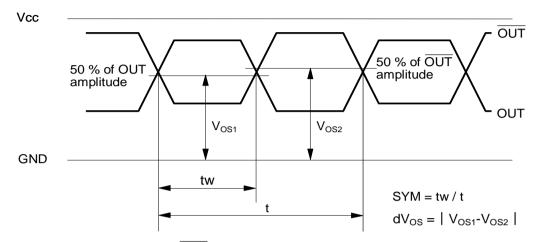

| Symmetry                    | SYM              | 45       | -        | 55       | %                       | At output crossing point                           |

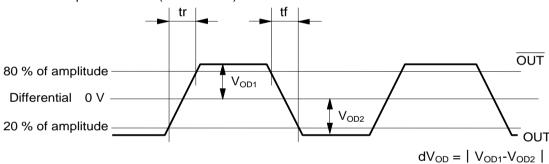

| Output voltage(LVDS)        | Vod              | 250      | _        | 450      | mV                      | -                                                  |

|                             | dVop             | -        | -        | 50       | mV                      | 1-                                                 |

|                             | Vos              | 1.15     | -        | 1.35     | V                       | 1-                                                 |

|                             | dVos             | -        | _        | 150      | mV                      | 1-                                                 |

| Output load condition(LVDS) | L_LVDS           | -        | 100      | -        | Ω                       | Connected between OUT and OUT                      |

| Input voltage               | V <sub>IH</sub>  | 70 % Vcc | -        | -        |                         | -                                                  |

|                             | V <sub>IL</sub>  | -        | -        | 30 % Vcc |                         | 1-                                                 |

| Rise time                   | t <sub>r</sub>   | -        | -        | 300      | ps                      | -                                                  |

| Fall time                   | tf               | -        | -        | 300      | ps                      | -                                                  |

| Start-up time               | t_str            | -        | -        | 3        | ms                      | -                                                  |

| Jitter                      | t <sub>DJ</sub>  | -        | 8.3      | -        | ps                      | Deterministic Jitter Vcc=2.5V                      |

|                             | T <sub>RJ</sub>  | -        | 0.8      | -        | ps                      | Random Jitter Vcc=2.5V                             |

|                             | t <sub>RMS</sub> | -        | 5.3      | -        | ps                      | δ(RMS of total distribution) Vcc=2.5V              |

|                             | t <sub>p-p</sub> | -        | 22       | -        | ps                      | Peak to Peak Vcc=2.5V                              |

|                             | t <sub>acc</sub> | -        | 1.1      | -        | ps                      | Accumulated Jitter(δ) n=2 to 50000 cycles Vcc=2.5V |

| Phase jitter                | t <sub>PJ</sub>  | -        | 0.34     | -        | ps                      | Offset Frequency: 12kHz to 20MHz Vcc=2.5V          |

| Phase noise                 | L(f)             | -        | -53      | -        | dBc/Hz                  | Offset 1Hz Vcc=2.5V                                |

|                             |                  | -        | -85      | -        | dBc/Hz                  | Offset 10Hz Vcc=2.5V                               |

|                             |                  | -        | -111     | -        | dBc/Hz                  | Offset 100Hz Vcc=2.5V                              |

|                             |                  | -        | -123     | -        | dBc/Hz                  | Offset 1kHz Vcc=2.5V                               |

|                             |                  | -        | -132     | -        | dBc/Hz                  | Offset 10kHz Vcc=2.5V                              |

|                             |                  | -        | -138     | -        | dBc/Hz                  | Offset 100kHz Vcc=2.5V                             |

|                             |                  | -        | -138     | -        | dBc/Hz                  | Offset 1MHz Vcc=2.5V                               |

| Frequency aging             | f_age            | -5       | -        | 5        | x10 <sup>-6</sup> /Year | 25 °C, 1st year                                    |

|                             |                  | _        | -        | _        |                         | -                                                  |

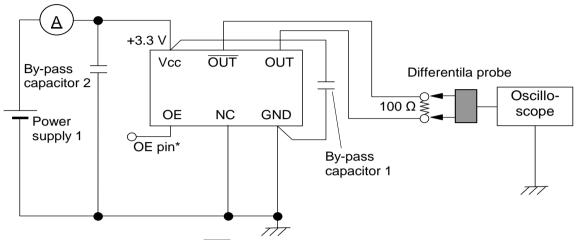

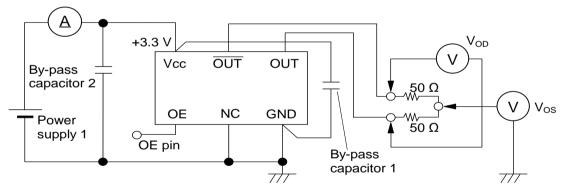

#### 3.Test circuit

1) To observe waveform and current (case 1)

- \* The lines from OUT and OUT pin are same length.

- \* To measure the disable current, OE pin is connected to GND

#### 2) To observe waveform and current (case 2)

\* The lines from OUT and OUT pin are same length.

- 3) Measurement condition

- A) Oscilloscope

- •Bandwidth should be 5 times higher than DUT's output frequency (4 GHz).

- •Probe ground should be placed closely from test point and lead length should be as short as possible.

- B) By-pass capacitor 1 (approx. 0.01  $\mu F$  to 0.1  $\mu F$ ) places closely between Vcc and GND.

- C) By-pass capacitor 2 (approx. 10  $\mu F$ ) places closely between power supply terminals on the board.

- D) Use the current meter whose internal impedance value is small.

- E) Power supply

- Start up time (0 Vg90 %Vcc) of power source should be more than 150  $\mu$ s and slew rate should be less than 19.8 mV/ $\mu$ s.

- Impedance of power supply should be as low as possible.

# 4. Timing chart

Each output waveform (OUT, and OUT)

Differential output waveform (OUT - OUT)

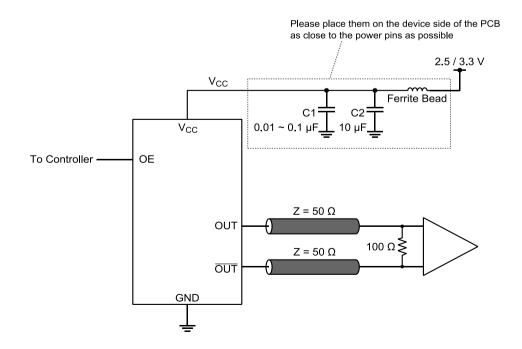

## 8. Example of schematic layout

This figure shows an example of this product's application schematic.

As with any high speed analog circuitry, the power supply pins for this device are vulnerable to noise. In order to achieve optimum jitter performance, power isolation with filter device is required for power supply pins.

In order to achieve best performance of the power isolation filter, it is recommended that the filter composing devices is placed on the device side of the PCB as close to the power pins as possible. The component value of this filter is just an example, it may have to be adjusted.

- $^*$  By-pass capacitor (approx. 0.01  $\mu\text{F}$  to 0.1  $\mu\text{F}$ ) places closely between Vcc and GND.  $^*$  By-pass capacitor (approx. 10  $\mu\text{F}$ ) places closely between power supply terminals on the board.  $^*$  Please design the two output lines by characteristic impedance 100  $\Omega$  and same length, and try to make the output lines as short as possible.

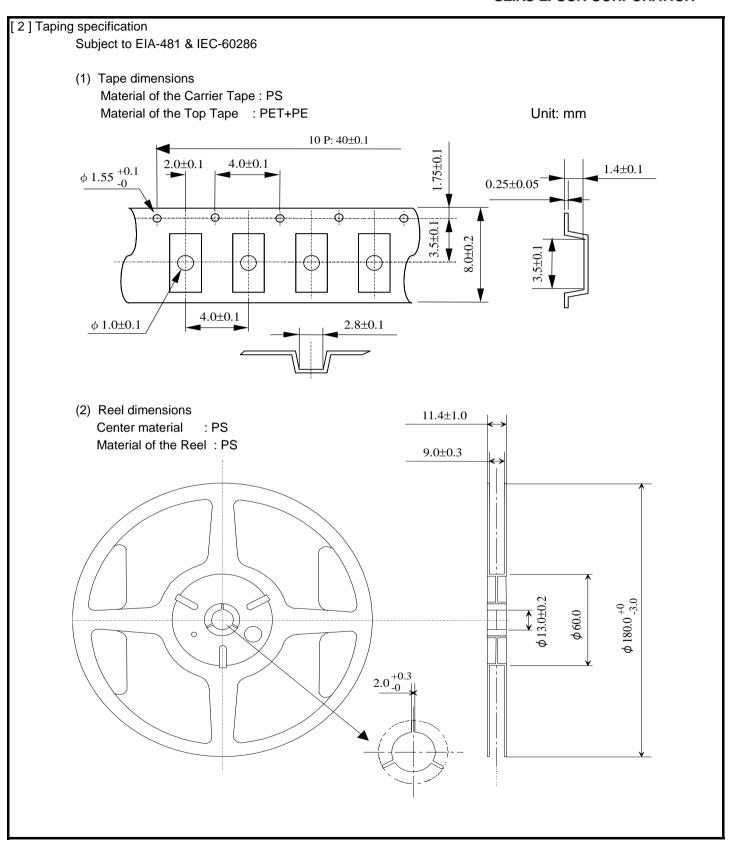

| [ 1 ]Droduo | t pumbor l | act 2 digita and (/w/) description          |      | The recommended code is "00" |

|-------------|------------|---------------------------------------------|------|------------------------------|

| [ 1 ]F10duc |            | ast 2 digits code(xx) description 2410113xx |      | The recommended code is 00   |

|             | Code       | Condition                                   | Code | Condition                    |

|             | 01         | Any Q'ty vinyl bag(Tape cut)                | 13   | 500pcs / Reel                |

|             | 11         | Any Q'ty / Reel                             | 14   | 1000pcs / Reel               |

|             | 12         | 250pcs / Reel                               | 00   | 2000pcs / Reel               |

## 10.Notice

- This material is subject to change without notice.

- Any part of this material may not be reproduced or duplicated in any form or any means without the written permission of Seiko Epson.

- The information about applied circuitry, software, usage, etc. written in this material is intended for reference only. Seiko Epson does not assume any liability for the occurrence of infringing on any patent or copyright of a third party. This material does not authorize the licensing for any patent or intellectual copyrights.

- When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- You are requested not to use the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes. You are also requested that you would not make the products available to any third party who may use the products for such prohibited purposes.

- These products are intended for general use in electronic equipment. When using them in specific applications that require

extremely high reliability, such as the applications stated below, you must obtain permission from Seiko Epson in advance.

- / Space equipment (artificial satellites, rockets, etc.)

- / Transportation vehicles and related (automobiles, aircraft, trains, vessels, etc.)

- / Medical instruments to sustain life

- / Submarine transmitters

- / Power stations and related

- / Fire work equipment and security equipment

- / Traffic control equipment

- / And others requiring equivalent reliability.

- All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective.

## 11.Contact us

http://www5.epsondevice.com/en/contact/